Добавление testbench'ей на языке Verilog в проект Vivado — различия между версиями

Материал из SRNS

Korogodin (обсуждение | вклад) |

Korogodin (обсуждение | вклад) |

||

| Строка 16: | Строка 16: | ||

| + | Наша задача разбивается на несколько этапов: | ||

| + | * написать код самих TB'ей, запустить, получить результаты, | ||

| + | * понять, какие файлы охватывает TB, | ||

| + | * внести изменения в скрипт регенерации проекта так, чтобы сохранились все настройки и файлы TB. | ||

| + | |||

| + | Приведу один из вариантов решения подзадач, не требующий знания tcl скриптов и опирающийся по-максимуму на GUI. | ||

| + | |||

| + | == Написание TB'ей == | ||

| + | |||

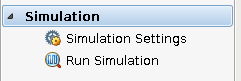

| + | Накидаем через GUI новый TB. В ''Flow Navigator'' (это панель слева в Vivado) в разделе ''Simulation'' выбираем ''Simulation Settings'' | ||

| + | [[file:20160404_vivado_revolution2.png|center]] | ||

== Ссылки == | == Ссылки == | ||

Версия 17:50, 4 апреля 2016

|

Пусть у нас есть дизайн для Vivado, проект которого разворачивается в соответствии со статьей Vivado и Git. Возможно, это конечный дизайн, возможно - сабмодуль для другого дизайна. Процедура добавления test bench'ей (далее TB) отличаться не будет, поэтому дальнейшее рассмотрение продолжим на примере сабмодуля imitator.

Задача - добавить TB'и для модулей imitator'а, причем

- они должны храниться в СКВ и быть доступны всем разработчикам,

- имеются в виду TB'и на языке Verilog для симуляторов типа Vivado Simulator, ModelSim и т.д., а не тесты на языках Си или Matlab для Verilator'а.

Для конкретики, будем добавлять в дизайн imitator TB'и для двух модулей:

- imichnl_synthesizer, отвечающий за фазу несущей,

- imitator_channel, являющийся топ-модулем для одного канала имитатора и включающий в себя первый модуль.

Наша задача разбивается на несколько этапов:

- написать код самих TB'ей, запустить, получить результаты,

- понять, какие файлы охватывает TB,

- внести изменения в скрипт регенерации проекта так, чтобы сохранились все настройки и файлы TB.

Приведу один из вариантов решения подзадач, не требующий знания tcl скриптов и опирающийся по-максимуму на GUI.

Написание TB'ей

Накидаем через GUI новый TB. В Flow Navigator (это панель слева в Vivado) в разделе Simulation выбираем Simulation Settings